# Base Resistance Contributions in SiGe HBT Devices

F. Stein

Advisors ST: N. Derrier, D. Céli

Advisor IMS: C. Maneux

### Outline \_\_\_

#### Base Resistance Contributions in SiGe HBT Devices

- Motivation why it is important to accurately determine R<sub>R</sub>

- Components of the base resistance how to partition R<sub>R</sub>

- Dual base tetrode device description of test structure

- Measurement conditions how to perform on wafer measurements

- Extraction method how to obtain R<sub>B</sub> and its components

- Extraction results using recent bipolar technology application to B5T

- Process split results and variation encountered errors & statistics

- Extraction results using TCAD simulation method robustness

- Conclusion

### Motivation 3

### why it is important to accurately determine $R_{R}$

resistances to be determined before model extraction of currents and AC characteristics

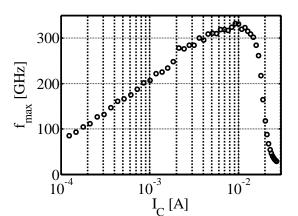

R<sub>B</sub> has significant impact on device speed (f<sub>max</sub>) and noise behaviour (NFmin)

$$f_{\rm max} \approx \sqrt{\frac{f_T}{8\pi R_B C_{BC}}}$$

\w

$$f_T = \frac{g_m}{2\pi(C_\pi + C_\mu)}$$

HICUM L2

equivalent circuit

# Components of the base resistance

### how to partition $R_{\rm B}$

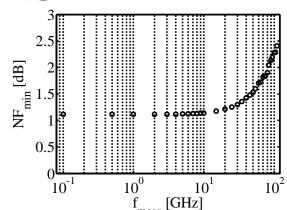

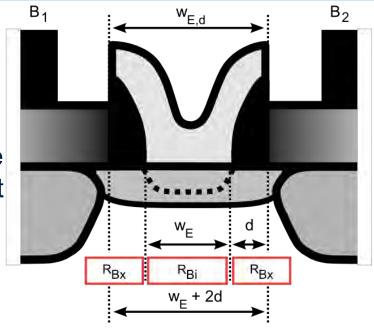

- base resistance is composed of the intrinsic base resistance  $R_{Bi}$  and the extrinsic base resistance  $R_{Bx}$

- intrinsic: bias dependent internal base sheet resistance  $r_{SBi}$

- extrinsic: from the inner base (emitter window edge) to the base contact

- including involved contact resistance (base link region) below the spacer

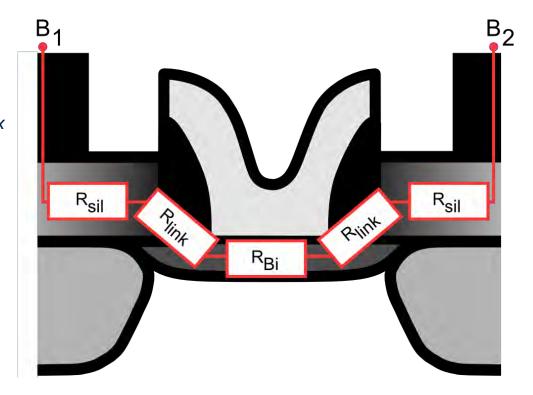

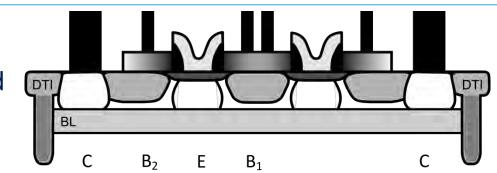

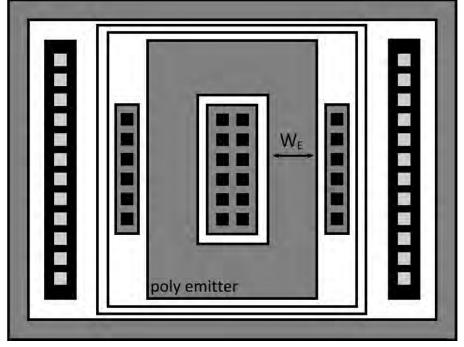

### Dual base tetrode device

### description of test structure

- dual base test structures present an improved approach compared to classical pinch-resistor structures (as presented in [1])

- extract the sheet resistance value of each component using simple yet accurate DC measurements

- two base terminals B1 and B2 independently accessible

- ring emitter structure to electrically separate the two bases

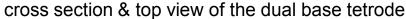

### Dual base tetrode device

### description of test structure

improvements over the original device structure include kelvin type connection to cancel out contact resistances

independent force and sense ports shorted in M1 layer improve measurement accuracy

usually  $>2\Omega$  contact resistance per probe

increased measurement complexity using 6 probes for biasing of test structure

### Dual base tetrode device

### description of test structure

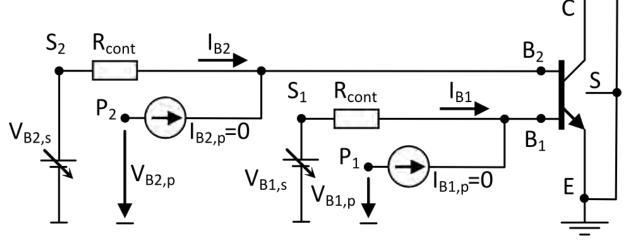

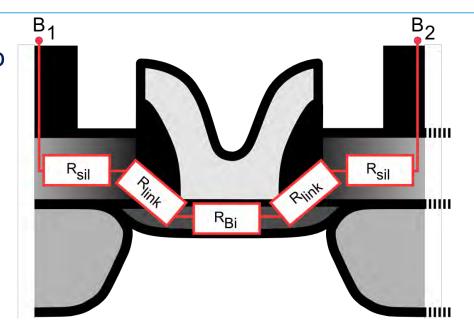

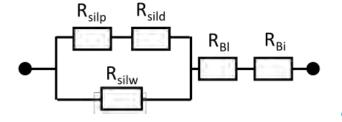

simplified equivalent circuit due to kelvin type connection

equivalent circuit of tetrode structure with individual base contacts

resistance contributions measured suitable for xtr

$$R_{meas} = \frac{V_{B2,p} - V_{B1,p}}{(|I_{B1}| + |I_{B2}|)/2}$$

$$= R_{Bx} + R_{Bi}/2$$

resistance contributions measured between B1 and B2

### Measurement conditions -

### how to perform on wafer measurements

- forcing probe (P) ports to zero current to ensure proper kelvin measurement and measurement of applied bias at M1 level

- differential bias applied on force port with constant ΔV<sub>B</sub> (40mV)

$$\Delta V_B = V_{B2,s} - V_{B1,s}$$

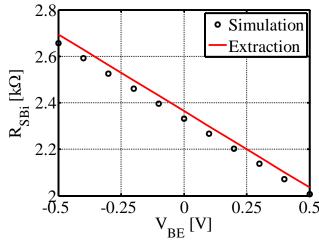

- bias conditions for V<sub>BE</sub>: -0.5 .. 0.5V

- avoid breakdown in reverse bias

- avoid active BE junction in forward mode

- measured resistance calculated using voltage of floating probes (P)

$$R_{meas} = \frac{V_{B2,p} - V_{B1,p}}{(|I_{B1}| + |I_{B2}|)/2} \text{ \w I}_{probe} = 0$$

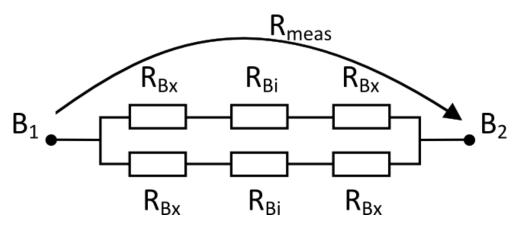

• the two contributions measured in each structure ( $R_{Bi}$  and  $R_{Bx}$ ) are best seen in the equivalent circuit (two parallel series resistances)

### how to obtain $R_B$ and its components

- extraction is based on geometry scaling approach

- R<sub>Bx</sub> is assumed to be constantfor a variation of the device length and independent of bias conditions  $[R_{Bx} = f(I_F)]$

- intrinsic base resistance is a function of all factors  $[R_{Bi} = f(w_F, I_F, V_{BF})]$

$$R_{meas}^{i,j,k} = R_{Bx}(l_E^j) + \frac{R_{Bi}(w_E^i, l_E^j, V_{BE}^k)}{2}$$

as in [2]

- two lengths per emitter width structure to cancel out the corner effects

- subtraction of the current of two structures gives the current of a inner, two-dimensional structure with an effective device length of  $\Delta I_F$

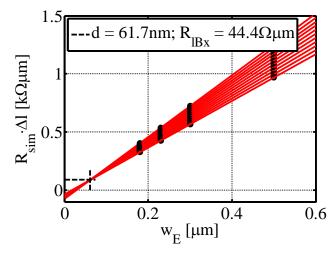

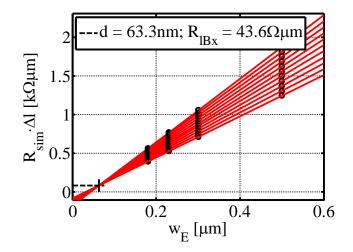

$$R_{meas}^{i,j,k} \cdot \Delta l_E = \frac{R_{sBi}(V_{BE}^k) \cdot (w_E^i - 2d)}{2} + R_{Bx} \cdot \Delta l_E$$

### how to obtain $R_B$ and its components

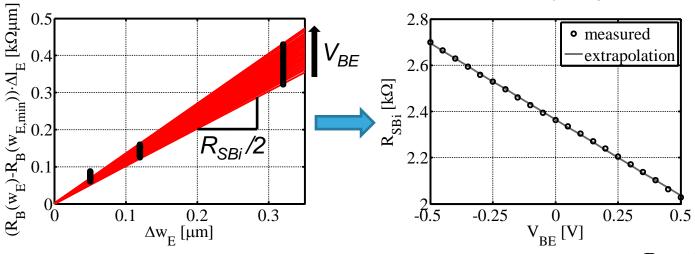

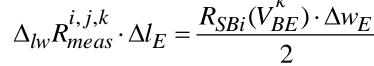

- $R_{meas}\Delta I_F$  curve may be normalized by a  $w_F$  reference structure

- smallest  $w_F$  structure used for suppression of undesired corner effects

- deduction of this reference yields a corrected  $\Delta_{lw}R_{meas}$  normalized by  $\Delta I_F$  versus a relative emitter width  $\Delta w_F$

- no need to be corrected by the electrical emitter width (compensation by d)

linear regression must cross the origin

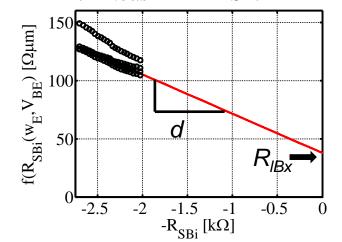

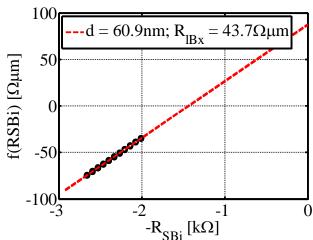

### how to obtain $R_B$ and its components

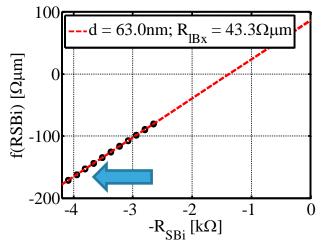

- compensate for parasitic corner effects and layout by electrical intrinsic base resistance width with  $w_{E,eff} = w_{E,d}$ -2d

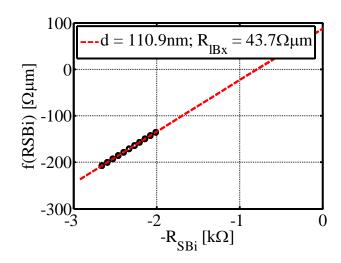

- extraction from normalized measured base resistance versus negative bias dependent internal base resistance

$$f(R_{SBi}) = R_{SBi}(V_{BE}^{k}) \cdot d + R_{LBx} = \dots$$

$$\dots = \Delta_{l} R_{meas}^{i,j,k} \Delta l_{E} - R_{SBi}(V_{BE}^{k}) \cdot w_{E} / 2$$

| $R_{SBi0}[k\Omega]$ | d [nm] | $R_{IBx}[\Omega \cdot \mu m]$ |

|---------------------|--------|-------------------------------|

| 2.37                | -35.6  | 36.8                          |

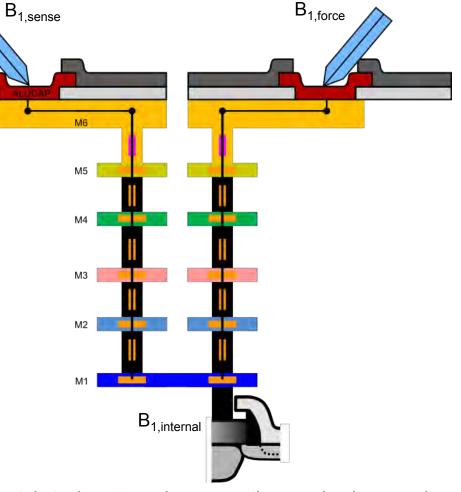

### how to obtain $R_B$ and its components

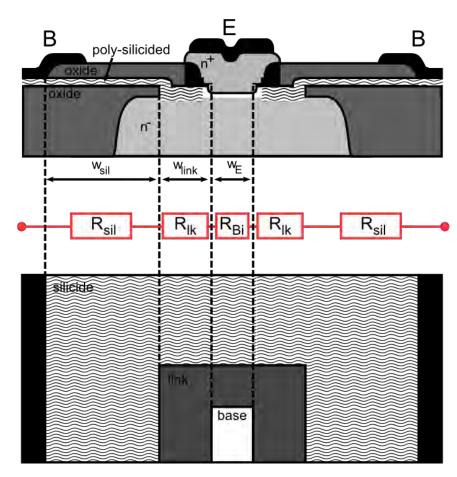

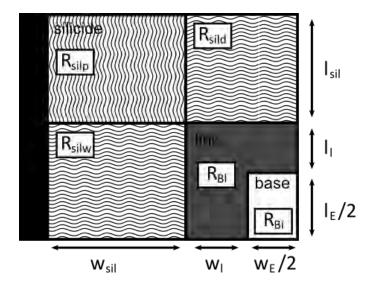

- external resistance contributions to determine:

- silicided external base region: R<sub>sil</sub>

- base-link region below spacer: R<sub>link</sub>

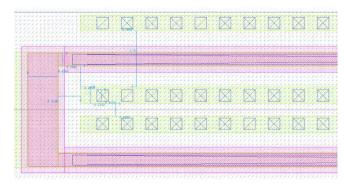

- partitioning of external contribution using information from DRM and layout

$$R_{Bx} = R_{sil} + R_{link}$$

- DRM process information: sheet resistance of silicided  $10\Omega/\Box$

- w<sub>sil</sub> = 335nm (from layout)

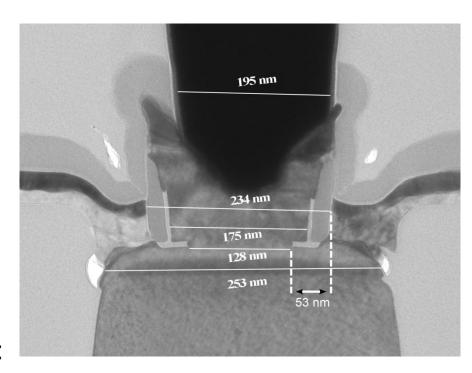

cross section & layout view of tetrode

#### how to obtain $R_B$ and its components

- determining spacer information from TEM imaging w<sub>link</sub>=53nm

- $R_{I,link} = R_{IBx} R_{I,sil} = 33.45 \Omega \mu m$

- $R_{slink} = 631\Omega/\Box$

- supplemental information from TEM imaging for device simulation:

- difference of drawn dimensions and actual dimensions on silicon of process

cross section of SiGe HBT with  $w_F = 0.18 \mu m$ obtained from TEM imaging analysis

# Process split results and variation 14

#### encountered errors & statistics

- extrapolation of the extrinsic base resistance times unit length  $R_{IBx}$  as well as the geometry correction d is performed far from the origin

- small measurement errors or abnormalities in geometry scaling may yield unphysical extraction results

- idea to study the impact of die-to-die variation and quantify uncertainty caused by the extraction routine

- technology parameter variation in process split served for trial

- measurement and automated extraction on 42 dies per process split

| Base width               | 5nm (reference) |                 |      |      |

|--------------------------|-----------------|-----------------|------|------|

| T <sub>anneal</sub> [°C] | -               | 1010            | 1025 | 1040 |

| Wafer                    | W02             | W05             | W07  | W12  |

| Base width               | 3nm (thir       | 3nm (thin base) |      |      |

| T <sub>anneal</sub> [°C] | -               | 1010            | 1025 | 1040 |

| Wafer                    | W14             | W17             | W20  | W24  |

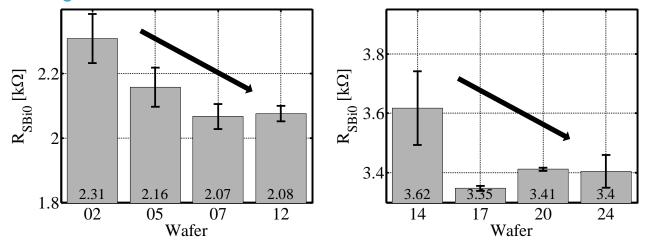

# Process split results and variation 15

#### encountered errors & statistics

- measurement and automated extraction on 42 dies per process split

- average value with the standard deviation for each wafer

- extracted zero-bias base sheet resistance  $(R_{SBio})$  is found to be highly increased for the thin base profile

- determination of  $R_{SBi}$  seems robust and yields feasible results

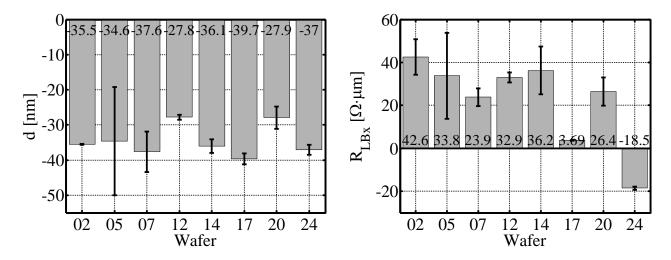

# Process split results and variation 16

#### encountered errors & statistics

questionable results obtained for geometry correction and extrinsic base resistance  $R_{IBX}$

• possibility of unphysical (negative) resistance value

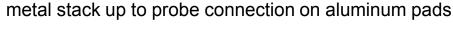

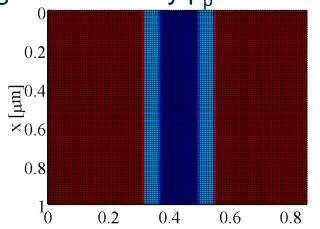

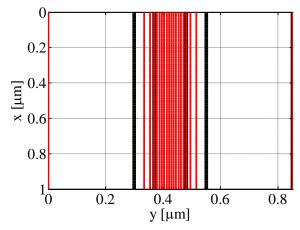

#### method robustness

- 1D numerical device simulation of tetrode structures [3]

- device structure according to layout combined with additional information on spatial dimensions from TEM imaging

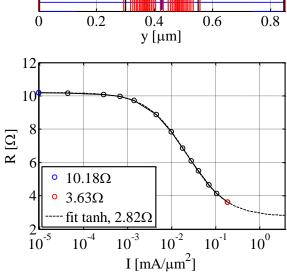

variable sheet resistance modeled through hole mobility  $\mu_p$

cross section & top view of one side of the tetrode

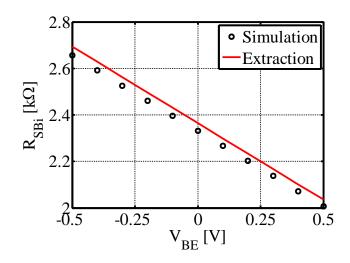

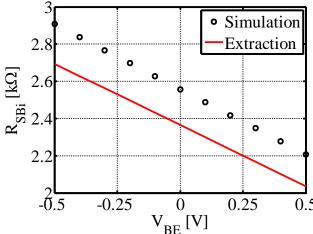

#### method robustness

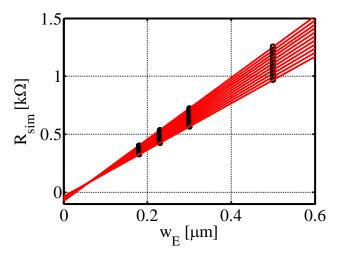

- simulation vs. bias for different device geometries according to silicon specifications of B5T device generation

- application of extraction routine to simulated data

- structure simulated with extracted average values of process split W02

| $R_{SBi0}[k\Omega/\Box]$ | $R_{Ssil}\left[\Omega/\square\right]$ | $R_{Slink}[\Omega/\Box]$ |

|--------------------------|---------------------------------------|--------------------------|

| 2.37                     | 10                                    | 740                      |

first trial with given electrical dimensions from DRM [ $w_{E,d}$  = 0.18, 0.23, 0.3, 0.5 µm]

#### method robustness

### extraction result yields expected quantities:

|       | $R_{SBi0}[k\Omega]$ | d [nm] | $R_{IBx}[\Omega \cdot \mu m]$ |

|-------|---------------------|--------|-------------------------------|

| input | 2.37                | 53     | 42                            |

| xtr   | 2.33                | 61     | 44                            |

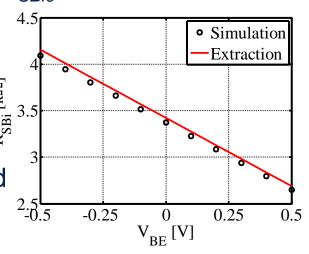

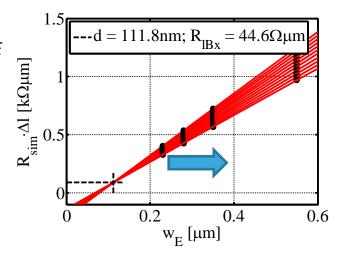

#### method robustness

extraction result for case of W14:

|       | $R_{SBi0}[k\Omega]$ | d [nm] | $R_{IBx}[\Omega \cdot \mu m]$ |

|-------|---------------------|--------|-------------------------------|

| input | 3.42                | 53     | 42                            |

| xtr   | 3.37                | 63     | 43                            |

• even though the  $R_{SBiO}$  value is about 50%

larger (thus further from the origin) the extraction result is in accordance with the expected results

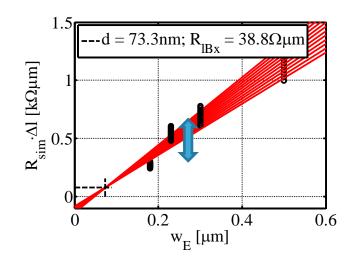

#### method robustness

- wrong measure for emitter window width w<sub>E</sub>

- constant offset of  $\Delta w_F = 50$ nm

|       | $R_{SBi0}[k\Omega]$ | d [nm] | $R_{IBx}[\Omega \cdot \mu m]$ |

|-------|---------------------|--------|-------------------------------|

| input | 2.37                | 53     | 42                            |

| xtr   | 2.33                | 111    | 44                            |

- method efficiently corrects the emitter

- window width difference that was added intentionally

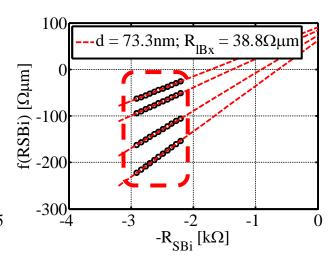

#### method robustness

- Random variation of measured resistance

- intentionally induced 'noise' on R<sub>meas</sub>

|       | $R_{SBi0}[k\Omega]$ | d [nm] | $R_{IBx}[\Omega \cdot \mu m]$ |

|-------|---------------------|--------|-------------------------------|

| input | 2.37                | 53     | 42                            |

| xtr   | 2.56                | 73.3   | 39                            |

• f(RSBi) vs. –R<sub>SBi</sub> curves not superimposed anymore

impact on emitter window width extraction as well as R<sub>SBiO</sub> value

#### method robustness

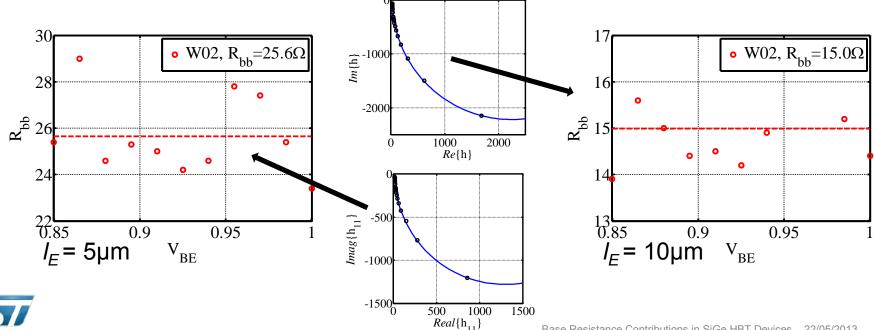

- simulation of 2D device structure to compare results with RB extraction from semi-circle method [4, 5, 6] on RF msmt structure for  $W_F = 0.18 \mu \text{m}$  and  $I_F = 5 \mu \text{m}$  as well as  $I_F = 10 \mu \text{m}$

- limited resolution of S-parameter based approach

- impact of self heating at high current to be taken into account [T↑ => R↑]

#### method robustness

total base resistance obtained from simulation of 2D device structure in low injection yields feasible results for both geometries

#### method robustness

comparison with calculated resistance using extracted sheet resistance values of W02 with analytical calculation of  $R_B$  [7]

$$I_E$$

= 5um  $I_E$  = 10um

$$R_{silw} = 0.3\Omega$$

$R_{silw} = 0.2\Omega$

$$R_{sild} = 1.9\Omega$$

$R_{sild} = 1.9\Omega$

$$R_{silp} = 1.4\Omega$$

$R_{silp} = 1.4\Omega$

$$R_{lc} = 433\Omega$$

$R_{lc} = 433\Omega$

$$R_{lw} = 4.1\Omega$$

$R_{lw} = 2.0\Omega$

$$R_{BI} = 4.1\Omega$$

$R_{BI} = 2.0\Omega$

$$R_{Bx} = 4.4\Omega$$

$R_{Bx} = 2.2\Omega$

good agreement with device simulation

### Conclusion •

- intrinsic base sheet resistance  $R_{SBiO}$  increasing with device generation and process improvements for high speed

- · extraction of extrinsic contributions far from origin hence prone to failure

- further investigation of impact of msmt accuracy and process scalability on existing extraction methods

- · appropriate structure already gives good results, what can be improved

- further improvement of extraction methods for more robust flow

- to be tested: automatic correction of geometrical information (esp. w<sub>E</sub>) using dispersion of measured data from regression analysis to overcome scaling issues

- a special thanks goes to P. Chevalier and E. Canderle for providing the process split wafers

# Thank you for your attention!

### Literature

- [1] H. M. Rein, M. Schroter, "Experimental determination of the internal base sheet resistance of bipolar transistors under forward-bias conditions", Solid-State Electron., vol. 34, no. 3, pp. 301–308, 1991.

- [2] C. Raya et al., "Scalable Approach for HBT's Base Resistance Calculation", IEEE Transactions on Semiconductor Manufacturing, vol. 21, pp. 186-194, 2008.

- [3] M. Schroter, "DEVICE, A Mixed Mode Simulator for Three-Dimensional Heterostructure Semiconductor Devices and Circuits", 2006.

- [4] W. M. C. Sansen and R. G. Meyer, "Characterization and measurement of the base and emitter resistance of bipolar transistors," IEEE J. Solid-State Circuits, No. 6, pp. 492-498, 1972.

- [5] T. Nakadai, Hashimoto, K., "Measuring the base resistance of bipolar transistors", Proc. BCTM 1991, pp. 200-203, 1991.

### Literature 29

- [6] W.J. Kloosterman, J.C.J. Paasechens and D.B.M Klaassen, "Improved Extraction of Base and Emitter Resistance from Small-Signal High-Frequency Admittance Measurements", BCTM, pp. 93-96, 1998.

- [7] M. Schroter, J. Krause, S. Lehmann and D. Celi, "Compact Layout and Bias-Dependent Base-Resistance Modeling for Advanced SiGe HBTs", IEEE Trans. on Electron Dev., vol 55, pp. 1693 -1701, 2008.